【導(dǎo)讀】針對(duì)目前雜散電感提取方法存在的問(wèn)題,本文提出了一種適用于SiC MOSFET換流回路雜散電感的提取方法,并基于SiC功率器件的開(kāi)關(guān)瞬態(tài)特性測(cè)試平臺(tái)對(duì)本文所提雜散電感提取方法的可行性進(jìn)行了驗(yàn)證。與現(xiàn)有的間接測(cè)量方法不同,該方法是基于SiC MOSFET開(kāi)關(guān)瞬態(tài)振蕩頻率求解換流回路雜散電感。

摘要

新能源電力系統(tǒng)國(guó)家重點(diǎn)實(shí)驗(yàn)室(華北電力大學(xué))的研究人員謝宗奎、柯俊吉等,在2018年第21期《電工技術(shù)學(xué)報(bào)》上撰文指出,在基于碳化硅(SiC)MOSFET器件的高壓高頻變換器中,快速的開(kāi)關(guān)瞬態(tài)電流變化率di/dt會(huì)作用于換流回路雜散電感上,導(dǎo)致SiC MOSFET器件承受較大的電氣應(yīng)力,增加系統(tǒng)電磁干擾。因此,換流回路雜散電感的準(zhǔn)確提取對(duì)于分析器件的開(kāi)關(guān)特性非常關(guān)鍵。

所以,該文提出了基于開(kāi)關(guān)振蕩頻率的換流回路雜散電感提取方法,該方法具有不受雜散電阻、測(cè)量延時(shí)和平臺(tái)尺寸的限制等優(yōu)點(diǎn)。最后將該方法與現(xiàn)有的不同雜散電感提取方法進(jìn)行了對(duì)比,驗(yàn)證了其有效性。

由于SiC功率器件具有電流密度高、開(kāi)關(guān)速度快、導(dǎo)通電阻小、阻斷電壓高等優(yōu)勢(shì)[1,2],已被逐漸應(yīng)用在光伏逆變器[3]、風(fēng)力發(fā)電、電動(dòng)汽車[4]等領(lǐng)域。與硅IGBT相比,SiC MOSFET的開(kāi)關(guān)速度更快,導(dǎo)致其對(duì)雜散電感更加敏感,在開(kāi)關(guān)過(guò)程中容易帶來(lái)嚴(yán)重的問(wèn)題,如開(kāi)關(guān)振蕩[5]、電磁干擾(Electromagnetic Interference, EMI)[6]和額外的功率損耗以及電氣應(yīng)力[7,8]。

為了預(yù)估器件在開(kāi)關(guān)過(guò)程中所受電氣應(yīng)力,并為實(shí)際應(yīng)用提供測(cè)試參考,需要對(duì)SiC MOSFET換流回路雜散電感進(jìn)行準(zhǔn)確提取。

目前,雜散電感的提取方法主要可以分為4類:解析法、數(shù)值計(jì)算法、直接測(cè)量法和間接測(cè)量法。

解析法主要是通過(guò)電感計(jì)算的理論公式,同時(shí)根據(jù)待測(cè)物體的相關(guān)參數(shù)對(duì)待測(cè)物體的雜散電感進(jìn)行估算。這種方法一般只適用于極少數(shù)特定的規(guī)則導(dǎo)體或直流母排,而對(duì)于多段結(jié)構(gòu)各異導(dǎo)體和器件組成的換流回路,其雜散電感通常很難進(jìn)行計(jì)算[9]。

數(shù)值計(jì)算法主要依賴于有限元分析或部分元等效電路方法來(lái)解麥克斯韋方程(如ANSYS Q3D Extractor)。此方法根據(jù)被測(cè)物體的幾何尺寸和材料信息來(lái)分析計(jì)算電感和電容[10-12]。

然而,當(dāng)被測(cè)物體的物理結(jié)構(gòu)變得復(fù)雜時(shí),該方法不但計(jì)算時(shí)間長(zhǎng),而且收斂性差。此外,若仿真過(guò)程中設(shè)置的電流路徑與實(shí)際的電流路徑不同,就會(huì)導(dǎo)致仿真結(jié)果與實(shí)際值存在偏差。

直接測(cè)量法又可以分為時(shí)域反射測(cè)量和頻域阻抗測(cè)量?jī)煞N方法。時(shí)域反射法基于傳輸線理論,并從延遲時(shí)間的反射信號(hào)中提取寄生電感[13],但復(fù)雜的實(shí)驗(yàn)設(shè)置、特殊硬件以及多步迭代過(guò)程限制了其應(yīng)用范圍。

阻抗測(cè)量方法使用阻抗分析儀對(duì)待測(cè)對(duì)象的兩個(gè)端子之間的阻抗進(jìn)行測(cè)量[14-16],但這種方法目前僅限于待測(cè)對(duì)象兩個(gè)端子之間的單端口測(cè)量。當(dāng)其他端子保持懸空狀態(tài)時(shí),懸空端子和大地之間的感應(yīng)電容會(huì)對(duì)阻抗測(cè)量造成影響,引入測(cè)量誤差。此外,這種測(cè)量方法所需的測(cè)量設(shè)備較為昂貴,并且對(duì)待測(cè)對(duì)象的尺寸有所限制。

現(xiàn)有的間接測(cè)量法主要是根據(jù)電感的伏安特性關(guān)系進(jìn)行求解,利用開(kāi)通或關(guān)斷漏源極電壓波形和對(duì)應(yīng)時(shí)間段的漏極電流波形來(lái)提取雜散電感。

根據(jù)對(duì)測(cè)量所獲取的電壓和電流波形進(jìn)行數(shù)學(xué)處理的方法不同,又可將現(xiàn)有的間接測(cè)量法分為微分法[8,17]和積分法[18-20]。其中,微分法對(duì)電流波形要求較高,而實(shí)驗(yàn)波形通常存在高頻紋波,導(dǎo)致不能準(zhǔn)確獲取電流變化率。

盡管積分法克服了微分法對(duì)電流波形形狀十分敏感的缺點(diǎn),但由于回路雜散電阻的存在,積分法積分區(qū)間選取的不同也會(huì)對(duì)雜散電感的提取結(jié)果產(chǎn)生影響。此外,這兩種方法都需要對(duì)電壓和電流進(jìn)行測(cè)量。

一般情況下,電流探頭都比較昂貴,而且測(cè)量帶寬遠(yuǎn)低于電壓探頭。并且這種基于電壓和電流波形的方法理論上要求電壓和電流波形之間沒(méi)有延時(shí)。因此這兩種間接測(cè)量方法可能適用于硅IGBT器件測(cè)試平臺(tái)雜散電感的提取。

但對(duì)于開(kāi)關(guān)速度較快的SiC MOSFET器件而言,其開(kāi)通和關(guān)斷的時(shí)間都只有幾十納秒,電壓和電流波形之間即使存在幾納秒的延時(shí)都會(huì)帶來(lái)很大的影響,而且現(xiàn)有高帶寬的電流探頭通常尺寸較大,成本較高。

針對(duì)目前雜散電感提取方法存在的問(wèn)題,本文提出了一種適用于SiC MOSFET換流回路雜散電感的提取方法,并基于SiC功率器件的開(kāi)關(guān)瞬態(tài)特性測(cè)試平臺(tái)對(duì)本文所提雜散電感提取方法的可行性進(jìn)行了驗(yàn)證。與現(xiàn)有的間接測(cè)量方法不同,該方法是基于SiC MOSFET開(kāi)關(guān)瞬態(tài)振蕩頻率求解換流回路雜散電感。

通過(guò)對(duì)SiC MOSFET開(kāi)關(guān)過(guò)程的振蕩階段進(jìn)行建模分析,推導(dǎo)出開(kāi)關(guān)振蕩頻率與回路雜散電感和雜散電容之間的關(guān)系。采用外部插入分立電容來(lái)人為地改變開(kāi)關(guān)振蕩頻率,從而構(gòu)造出包含電感和電容參量的數(shù)學(xué)方程組,通過(guò)消元法求解方程組,計(jì)算出換流回路的雜散電感。

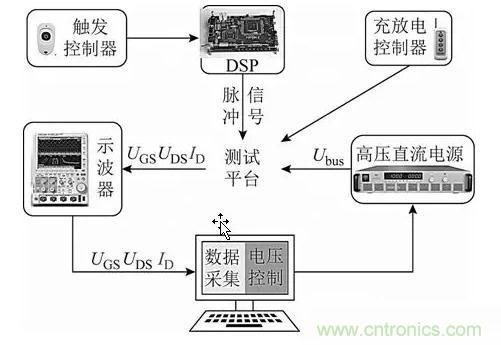

圖1:測(cè)試系統(tǒng)框圖