【導讀】在使用模數轉換器(ADC)進行設計時,人們很容易錯誤地認為,縮小輸入信號以滿足ADC的滿量程范圍,會造成信噪比(SNR)的明顯降低。

需要處理寬電壓擺幅的系統(tǒng)設計人員對此更是尤為關注。此外,與較高電壓供電的ADC相比,低壓供電(5V或更低)的ADC更是種類繁多。

較高電壓供電通常會導致更大的功耗和更復雜的電路板布局(例如,需要更多的去耦電容)。

本文將討論影響SNR損失(由信號縮放引入)的主要因素,如何對其進行定量分析,以及更重要的是:如何把這種影響降至最低。

傳感器或系統(tǒng)產生的許多信號都是雙極性高壓信號(如廣泛使用的±10V信號)。不過,有很多簡單的方法可以使這種信號通過ADC;也可以采用各種集成高壓ADC解決方案:可處理這種滿量程的大輸入信號,而又不犧牲SNR。這些解決方案需要極高的供電電壓來滿足輸入范圍的要求,并且其功耗也相當大(圖1)。這些高壓ADC還縮小了信號調理(運放)解決方案的選擇范圍。如果信號需要與高壓和低壓輸入組合多路復用,系統(tǒng)成本會大幅提升(圖2)。

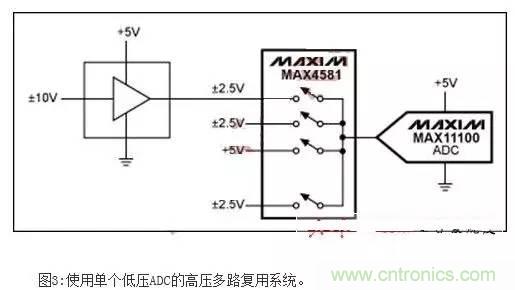

還可以使用輸入放大器對信號進行縮放,使其與低壓ADC的滿量程輸入范圍相符合。這種信號調理電路可以連接到一個多路復用輸入,從而使所有的信號都能與ADC的范圍相符合(圖3)。

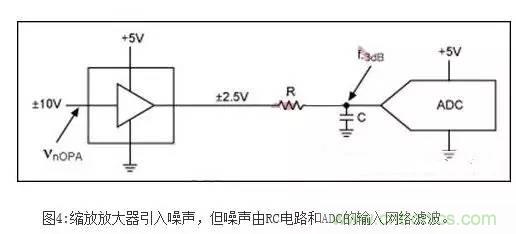

當使用放大器進行信號電壓縮放時,噪聲以放大器輸入為參考。此時,有兩個主要的噪聲源:放大器本身的輸入參考噪聲,以及ADC的縮小輸入參考噪聲。這兩個噪聲源按照二次項的方式組合。此外,放大器的噪聲還會通過ADC的輸入帶寬以及放大器與ADC輸入之間的抗混疊濾波器進行濾波,參見圖4.

圖4:縮放放大器引入噪聲,但噪聲由RC電路和ADC的輸入網絡濾波。

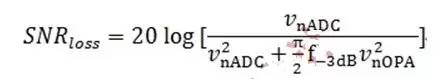

系統(tǒng)SNR(放大器輸入端)的計算公式為:

式中:VnADC為ADC的輸入RMS噪聲;VnOPA為放大器的輸入參考噪聲(輸入參考的X倍)=單極點-3dB頻率。

給定ADC的滿量程范圍、ADC的輸入參考噪聲和放大器的比例因子后,有兩個變量會影響到SNR損失降低的目標:濾波器的截止頻率和放大器的輸入參考噪聲。

如果信號源具有低頻分量,可以設計濾波器,使放大器能夠容許較大的輸入噪聲(較高的輸入噪聲通常與較低的功耗和成本有關)。如果ADC限制了系統(tǒng)的帶寬,放大器需要具有足夠低的輸入參考噪聲,以便把SNR損失控制在可接受的范圍內。

舉例來說,給定一個±10V輸入信號和一個SNR為92dB的5VP-P滿量程范圍ADC,則比例因子(輸入與滿量程范圍之比)為4.數據表中的ADC輸入參考噪聲為44.4nV RMS .假設濾波器的截止頻率為10kHz,放大器的輸入參考噪聲為10nV/ (Hz) 1/2,則SNR的損失為:SNR(loss)=0.035dB.

如果沒有濾波器,并假定ADC帶寬為10MHz,為了達到相同的SNR損失,所需的輸入參考噪聲則變?yōu)?.3nV/(Hz) 1/2,這一要求非常嚴格。

對于10MHz相同帶寬的ADC,如果允許SNR(loss)=0.5dB,則對放大器的噪聲要求為4nV/(Hz) 1/2,相對來說較容易實現。

因此,如果給定了系統(tǒng)帶寬和可容許的SNR損失,增加比例放大器以使高壓信號轉換到滿量程范圍的低壓ADC,將是完全可行的解決方案。當把多路不同擺幅的信號饋送到一個多路復用的低壓ADC時,這種解決方案能夠實現高性價比的系統(tǒng)。

推薦閱讀: